JANUARY 2015 VOL. 22, NO. 1 ISSN: 1074 1879

#### EDITOR-IN-CHIEF: M.K. RADHAKRISHNAN

#### TABLE OF CONTENTS

#### TECHNICAL BRIEFS.....1

- 2014 Nobel Prize in Physics

- •The Ubiquitous Blue Light Sources

- Symptom of 'the end' of Miniaturization for Micro/ Nanoelectronics

- 2014 IEEE International Electron Devices Meeting Highlights

#### UPCOMING TECHNICAL MEETINGS ..... 9

- 2015 IEEE Photovoltaic Specialists Conference (PVSC)

- 2015 IEEE International Vacuum Electronics Conference (IVEC)

#### SOCIETY NEWS ...... 11

- Message from EDS President

- Message from EDS Vice President of Technical Committees and Meetings

- Message from Editor-in-Chief

- Call for Nominations-IEEE Fellow Class of 2016

- Congratulations to the 34 EDS Members Recently Elected to IEEE Senior Member Grade

- 2013 George E. Smith Award Winner

- 2013 EDS Paul Rappaport Award

- EDS 2015 Ph.D. Student Fellowship Program

- EDS 2015 Masters Student Fellowship Program

####

- EDS-ETC—ED Universidad Santo Tomas Student Branch Chapter

- IEEE Benefits and Services for Students and Young Professionals

- QuestEDS

| CHAPTER NEWS                                                 |

|--------------------------------------------------------------|

| REGIONAL NEWS                                                |

| EDS MEETINGS CALENDAR                                        |

| 2014 EDS Bog MEETING RECAP AND<br>MAJOR INITIATIVES APPROVED |

# TECHNICAL BRIEFS

#### 2014 Nobel Prize in Physics

Isamu Akasaki

Hiroshi Amano

Shuji Nakamura

The prestigious 2014 Nobel Prize in the Physics was awarded to three former and current members of the IEEE and Electron Devices Society, Isamu Akasaki and Hiroshi Amano and Shuji Nakamura, "for the invention of efficient blue light-emitting diodes which has enabled bright and energy-saving white light sources." The prize, with an award of SEK 8M (£690,000), was shared by the three winners who received their medals at a ceremony in Stockholm on 10 December 2014.

In the 1980s Akasaki and Amano working at Nagoya University and Nakamura independently working at the Nichia Corporation focused on the growth of high quality compound semiconductor gallium nitride (GaN) thin films onto substrates. Both teams used metalorganic vapor phase epitaxy techniques to deposit GaN material which is ideal for blue light emission due to its large band-gap energy corresponding to ultraviolet light. Currently, Akasaki works at Meijo University and Nagoya University, Amano at Nagoya University, Nakamura at University of California, Santa Barbara.

The members of the IEEE Electron Devices Society should be very pleased by the fact that three members of our community were recognized for their device contributions with the 2014 Nobel Prize in Physics. In addition, they have been recognized with numerous awards for their achievements. GaN LEDs are now used in a wide range of applications, from televisions, mobile handheld devices, to street lighting.

> Paul Yu Jr. Past President IEEE Electron Devices Society

#### YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at radhakrishnan@ieee.org

#### ELECTRON DEVICES

#### SOCIETY

#### President

Albert Z.H. Wang University of California, Riverside E-mail: aw@ee.ucr.edu

President-Elect Samar Saha Ultrasolar Technology E-mail: samar@ieee.org

Treasurer Ravi M. Todi Qualcomm Technologies, Inc. E-mail: rtodi@ieee.org

Secretary Fernando Guarin **IBM Microelectronics** E-mail: guarinf@us.ibm.com

Jr. Past President Paul K.L. Yu University of California at San Diego E-mail: p.yu@ieee.org

Sr. Past President Renuka P. Jindal University of Louisiana at Lafavette E-mail: r.jindal@ieee.org

#### Vice President of Membership and Services

Mikael Ostling KTH, Royal Institute of Technology E-mail: mostling@kth.se

Vice President of Publications and Products Bin Zhao Fairchild Semiconductor E-mail: bin.zhao@ieee.org

Vice-President of Regions/ Chapters Xing Zhou Nanyang Technological University E-mail: exzhou@ntu.edu.sg

Vice President of Technical **Committees & Meetings** Leda Lunardi North Carolina State University E-mail: leda\_lunardi@ncsu.edu

**IEEE Newsletters** Theresa Smith **IEEE** Operations Center E-mail: tlsmith@ieee.org

**Executive Director** Christopher Jannuzzi **IEEE** Operations Center E-mail: c.jannuzzi@ieee.org

Membership Administrator Joyce Lombardini IEEE Operations Center E-mail: j.lombardini@ieee.org

#### NEWSLETTER

#### EDITORIAL STAFF

**Editor-In-Chief** M.K. Radhakrishnan NanoRel E-mail: radhakrishnan@ieee.org

REGIONS 1-6, 7 & 9 Eastern, Northeastern & Southeastern USA (Regions 1,2 & 3) Mukta Farooq IBM Systems and Technology E-mail: farooqm@us.ibm.com

Central USA & Canada (Regions 4 & 7) Peyman Servati University of British Columbia E-mail: peymans@ece.ubc.ca

Southwestern & Western USA (Regions 5 & 6) Adam M. Conway Lawrence Livermore Nat. Lab. E-mail: conway8@llnl.gov

#### Latin America (Region 9)

Joao Antonio Martino University of Sao Paulo E-mail: martino@lsi.usp.br

#### **REGION 8**

Eastern Europe Tomislav Suligoj University of Zagreb E-mail: tom@zemris.fer.hr

#### Scandinavia & Central Europe

Zygmunt Ciota Technical University of Lodz E-mail: ciota@dmcs.pl

UK, Middle East & Africa Jonathan Terry The University of Edinburgh E-mail: jonterry@ieee.org

Western Europe Jan Vobeckv Abb Switzerland Ltd. E-mail: vobecky@fel.cvut.cz

REGION 10 Australia, New Zealand & South East Asia P Susthitha Menon Universiti Kebangsaan Malaysia E-mail: psusthitha.menon.2009@ ieee.org

Northeast Asia Kunivuki Kakushima Tokyo Institute of Technology E-mail: kakushima@ep.titech.ac.jp

#### East Asia

Mansun J. Chan Hong Kong Univ. of Sc. & Tech. E-mail: mchan@ust.hk

South Asia

Manoj Saxena University of Delhi E-mail: msaxena@ieee.org

#### **CONTRIBUTIONS WELCOME**

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either the Editorin-Chief or appropriate Editor. The e-mail addresses of these individuals are listed on this page. Whenever possible, e-mail is the preferred form of submission.

| D. Camacho(1)A. Escobosa(2)Z. Celik-Butler(2)S. S. Iyer(2)R. Huang(1)S. Chung(2)M. Meyyappan(2)L. Lunardi(1)M. Farooq(1)A. Nathan(2)M. Ostling(2)P. Fay(1)M. Shur(2)M.K. Radhakrishnan(2)C. Lilley(1)D. Verret(1)J. Swart(1)D. Misra(1)B. Zhao(2)X. Zhou(2)H. S. Momose(1) | 2015                                                            | TERM                            | 2016                                                                   | TERM                            | 2017                                                                     | Term                                          |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------|-----------------------------------------------|---|

|                                                                                                                                                                                                                                                                            | S. S. Iyer<br>M. Meyyappan<br>A. Nathan<br>M. Shur<br>D. Verret | (2)<br>(2)<br>(2)<br>(2)<br>(1) | R. Huang<br>L. Lunardi<br>M. Ostling<br>M.K. Radhakrishnan<br>J. Swart | (1)<br>(1)<br>(2)<br>(2)<br>(1) | S. Chung<br>M. Farooq<br>P. Fay<br>C. Lilley<br>D. Misra<br>H. S. Momose | (2)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | - |

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

EDS Board of Governors (BoG)

**Elected Members-at-Large**

Elected for a three-year term (maximum two terms) with 'full' voting privileges

Newsletter Deadlines

**I**SSUE

| ISSUE   | <u>Due Date</u> |

|---------|-----------------|

| January | October 1st     |

| April   | January 1st     |

| July    | April 1st       |

| October | July 1st        |

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

IEEE Electron Devices Society Newsletter (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright © 2015 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

### GAN BASED BLUE LIGHT EMITTING DIODES AND LASERS

S. Mokkapati and C. Jagadish

2014 Nobel Prize in Physics highlights the impact efficient blue light sources have had on our lives. These light sources have penetrated almost every aspect of our lives. The first thing most of us look at when we wake up every day is probably a smart phone screen to check the time. Such displays would not have been possible without small, efficient blue light sources. Blue light emitting diodes (LEDs) are currently used to generate white light for energy efficient lighting applications. Lighting consumes ~20 % of our total electricity consumption. If we make a complete shift to LEDs for lighting applications, we would be reducing our energy consumption significantly. This will result in huge savings with minimal effort.

The journey from the first demonstration of LEDs to the first demonstration of blue LEDs spanned almost 85 years. The device concepts that were used for the initial demonstration of blue light sources were already developed and in fact, were used for demonstration of red/infrared light emitting diodes and lasers in the 1960s. However, it took 30 more years to be able to generate efficient blue light sources. We give a brief history of the developments that lead to the first blue light sources and developments following the first demonstrations. We will discuss the important milestones in the development of blue LEDs/lasers for each of the components below that are essential for any light emitting device:

- Semiconductor layers that efficiently convert electrons into light

- Strategies for electron and light confinement

- Efficient carrier injection and contact layers

ZnSe and SiC were the wide bandgap semiconductors initially

investigated in 1990s for blue light emission. GaN is a direct bandgap (3.4 eV) semiconductor that emits in the ultra-violet region. GaN exists in both cubic and hexagonal lattices. Good quality semiconductors for the active layer of light emitting devices are grown using epitaxial techniques. Lattice matching between the growth substrate and the epitaxial layers to be grown is an important criterion for the growth of high quality semiconductor layers. Lack of a lattice matched substrate for growth of GaN is still a significant issue for epitaxy of GaN and related compounds. Initial efforts on GaN epitaxial growth were based on sapphire substrates. Sapphire substrates are still used for GaN growth even though GaN substrates are available.

Initial growth studies of GaN were based on Hydride Vapour phase epitaxy (HVPE). Development of Molecular beam epitaxy (MBE) and Metal-**Organic Chemical Vapour Deposition** (MOVPE) in the 1970s proved to be a major milestone in the development of semiconductor light emitting devices. Isamu Akasaki began studies on MOVPE growth of GaN as early as 1974 at Matsushita Research Institute, Tokyo. He continued working on GaN growth with Hiroshi Amano when he moved to Nagoya University in 1981. Akasaki and Amano developed MOVPE for GaN growth on AIN buffer layers on sapphire substrates<sup>1,2</sup> and Shuji Nakamura at Nichia Chemicals developed the same growth technique for GaN on GaN buffer layers on sapphire substrates<sup>3</sup>. An optimized buffer layer reduced the interfacial energy between the GaN layers and the substrate and promoted lateral growth.

After successful demonstration of photoluminescence from GaN layers epitaxially grown on AIN or GaN buffer layers, the next step towards fabrication of electrically injected light emitters in the blue/UV region was to tackle the issue of p-doping. Researchers were able to dope the large bandgap semiconductors with donors (n-type), but acceptor (p-type) doping was still an unresolved issue that inhibited the development of blue light sources. Zn and Mg are used as acceptors for MOVPE growth of semiconductors. p-type behaviour in electron beam irradiated GaN was observed by Akasaki and Amano in late 1980s<sup>4</sup>. Understanding of the phenomenon was later developed by Nakamura who suggested that the acceptors form complexes with hydrogen and become inactive. A heat treatment or electron beam irradiation was necessary to activate the dopants. Successful understanding and demonstration of p-doping in GaN and related compounds, AlGaN, InGaN was an important step in the journey of blue/UV light sources. It enabled fabrication of p-n junctions and contact layers for the fabrication of blue/UV light sources.

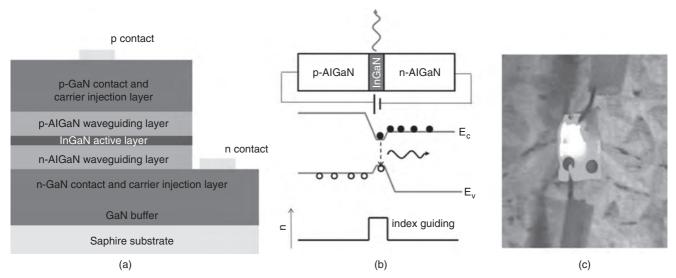

The first light emitting devices demonstrated were bulk devices. There is no photon confinement or mode confinement in such devices. A device concept that would allow carrier confinement and optical confinement in the active region and enable low threshold, room temperature lasing is the so called double heterojunction structure (Figure 1(a)). It uses a larger bandgap, lower refractive index barrier layers on either side of the active layer. The bandgap difference results in carrier confinement and the refractive index contrast results in optical confinement (Figure 1(b)). The next important conceptual development in the road towards efficient light emitters was that of introducing quantum confinement into the active region. Confinement

Fig 1. (a) Layer structure of a typical blue double heterostructure. (b) Carrier confinement due to lower bandgap and optical confinement due to higher refractive index in the InGaN region of InGaN/AIGaN double heterostructures. (c) Picture of an actual blue light emitting diode.

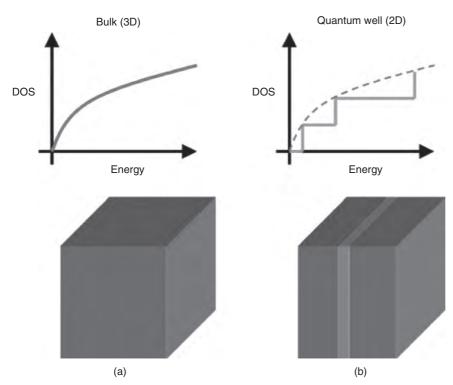

Fig 2. Parabolic density of states in bulk (a) and step function like density of states in a quantum well (b). The step function like density of states in quantum wells results in higher gain at a given carrier injection level resulting in higher output powers for a given input power.

of charge carriers in 1 dimension in what are known as quantum wells modifies the density of states from being a parabolic function of energy in bulk material to a step function in quantum wells (Figure 2). The altered density of states results in higher gain at any given carrier injection levels compared to bulk material, leading to low threshold, high power devices. Akasaki et. al. investigated AlGaN/GaN heterostructures while Nakamura et. al. investigated growth of InGaN quantum wells with GaN or AlGaN barriers. They first demonstrated LEDs based on these quantum wells<sup>5</sup>, followed by blue lasers in 1995–96<sup>6</sup>.

AIGaN/GaN heterostructures are used for emitters in the UV region. The emission wavelength can be relatively blue-shifted by increasing the Al content. Emission below 360 nm is challenging with AlGaN quantum wells due to increase in the strain in the AlGaN layers, which results in reduced radiative efficiency. Defect free AIGaN guantum wells with relatively higher Al content can be grown by using AIN strain reducing interlayers in the GaN buffer (grown on sapphire substrates) and emission in deep UV has been achieved using such structures. Alternatively, InAIGaN can be used because it is an efficient emitter below 360 nm due to In segregation effects.

InGaN quantum confined active regions are used for more efficient emission in the blue-green region of the visible spectrum. GaN or Alln(Ga)N are usually used as barriers for InGaN quantum well light emitting devices. Alln(Ga)N cladding layers result in blue-shifted emission with higher intensities from the InGaN quantum structures due to enhanced quantum confinement. Typical InGaN quantum well devices exhibit reduced efficiencies at higher injection currents due to carrier escape from the active region. This is a serious problem with high power lasers that typically operate at high injection densities. Use of AlGaN/ GaN multi quantum well barriers as carrier blocking layers has resulted in improved slope efficiency and reduced threshold currents in InGaN devices. The AIGaN/GaN barriers also reduce the effect of strain in the InGaN quantum well active region compared to quantum well structures capped with AIGaN. Use of Al containing super lattices in the GaN buffers (grown on sapphire substrates) has also resulted in improved device performance due to strain compensation and reduced threading dislocation density in the devices as Al containing layers act as filters for these dislocations.

Efforts are still ongoing to improve the quality of epitaxial layers used for blue/UV light sources. The crystallographic structure of wurtzite group-III nitrides induces a piezoelectric dipole across the typically c-axis oriented quantum structures in the active region of GaN based devices. The associated electric field leads to a spatial separation of electrons and holes and consequently results in reduced radiative recombination efficiency of the device. The piezoelectric dipole moment associated with the structures increases in magnitude with increasing In content in InGaN/GaN guantum wells, which is a serious issue for bluegreen emitters. The effects of piezoelectric polarization can be eliminated/reduced by growing III-nitride semiconductor structures on nonpolar (e.g. a-plane or m-plane GaN or r-plane sapphire) or semipolar (e.g. 1122 GaN) substrates. (AlInGa) N heterostructure devices grown on non-polar/semipolar directions have been demonstrated and show comparable or better performances than similar devices grown on polar substrates. Improving the efficiency of light extraction from high In content InGaN/GaN heterostructures seems to be the current focus of research involving GaN based light emitters. Enhanced light emission from long wavelength GaN based emitters has been demonstrated by coupling the quantum structures with surface plasmons or photonic crystal structures.

Current white LEDs rely on converting blue emission using phosphors. This results in inefficient colour rendering for the white LEDs. Colour mixing using red, blue and green LEDs would result in better colour rendering for white LEDs. Lack of efficient green LEDs is the current bottleneck for this application. Current efforts are focussed on realisation of Ill-nitride based high efficiency green LEDs by investigating novel semiconductor nanostructures like nanowires. Nanowires offer the possibilities of semiconductor growth on lattice-mismatched substrates and light extraction strategies into the active region.

#### References

- Amano, H.; Sawaki, N.; Akasaki, I.; Toyoda, Y. *Applied Physics Letters* **1986**, 48, (5), 353–355.

- Hiramatsu, K.; Itoh, S.; Amano, H.; Akasaki, I.; Kuwano, N.; Shiraishi, T.; Oki, K. *Journal of Crystal Growth* **1991**, 115, (1–4), 628-633.

- Nakamura, S. Japanese Journal of Applied Physics 1991, 30, (Part 2, No. 10A), 3.

- Hiroshi, A.; Masahiro, K.; Kazumasa, H.; Isamu, A. Japanese Journal of Applied Physics 1989, 28, (12A), L2112.

- Nakamura, S.; Mukai, T.; Senoh, M. *Applied Physics Letters* **1994**, 64, (13), 1687–1689.

- Nakamura, S.; Masayuki, S.; Shin-ichi, N.; Naruhito, I.; Takao, Y.; Toshio, M.; Hiroyuki, K.; Yasunobu, S. Japanese Journal of Applied Physics 1996, 35, (1B), L74.

**Chennupati Jagadish** is an Australian Laureate Fellow and Distinguished Professor in the Department of Electronic Materials Engineering, Research

School of Physics and Engineering, Australian National University, Canberra. He is currently serving as Vice-President and Secretary Physical Sciences of the Australian Academy of Science. He was an elected member of EDS BoG, Chaired EDS Optoelectronic Devices Technical Committee and Photovoltaic Devices Technical Committee and an Editor of IEEE Electron Device Letters.

Sudha Mokkapati is a Research Fellow in the same Department. She has served as a Australian Research Council (ARC) Super Science Fellow and ARC Post-

Doctoral Fellow. She has published widely in the areas of quantum dot optoelectronic devices, plasmonic solar cells and light trapping in solar cells and nanowire lasers.

S. Mokkapati and C. Jagadish Research School of Physics and Engineering of Australian National University Canberra, Australia sudha.mokkapati@anu.edu.au chennupati.jagadish@anu.edu.au

# SYMPTOM OF 'THE END' OF MINIATURIZATION FOR MICRO/NANOELECTRONICS

#### Hiroshi Iwai

At the beginning of 1970's, the first generation of microprocessors had been introduced with thousands of MOSFETs on a Si chip. This was the beginning of the 'microelectronics' and really the beginning of the technological revolution continuing for half a century. Now entering the 'smart society,' we have to deal with huge amount of information growing every year, and the demand for higher-performance and lowerpower-consumption microprocessors becomes stronger and stronger.

The most effective way for realizing the higher-performance and lower-power consumption—per operation—is to miniaturize the MOSFET, because it decreases the capacitance, and hence, results in decrease in the switching time and power consumption of the circuits. The operational voltage reduction accompanied with the miniaturization further decreases the power. That is the reason for the continuous downsizing of the MOS-FETs for 45 years until now.

The first generation in early 1970's was that of only p-channel MOSFETs (PMOS LSI) with 10  $\mu$ m design rule. At that time, even though 'Moore's law' had not been popular at all, and the 'scaling method' had not been published, DRAMs were the technology driver, and many semiconductor companies started to compete each other to decrease the bit cost by increasing the memory capacity at the rate of 4 times per 3 years. Then, the technology finally evolved to CMOS, and 'microelectronics' became 'nanoelectronics,' but still the Si MOS-

FET has been the device used for the circuits. During the period, the technology driver changed to logic LSI's and one generation shrinked to 2 years. The miniaturization has been continued for 19 generations until now as shown in Table 1, and that the area of one MOSFET decreased to quarter million times.

Very few people could predict such a tremendous success in the miniaturization, and there have been many predictions for the limit of the downsizing at 1, 0.5, 0.25 and 0.1  $\mu$ m, respectively. Very fortunately, new technologies ion-implantation, dry etching, metal/ high-k gate stack, SOI, fin-FET, etc.—, solved the problems, and the predictions turned out not to be true.

What would be the future? Table 2 shows the future predictions of the downsizing by ITRS 2013, published in April 2014. The downsizing will continue for future 7 generations with the shrink rate of 0.7 times every 2 years, and would reach '1.3 nm' in 2027. However, it is only for the 'commercial' name, and real 'physical' parameters such as the metal half pitch and gate length in 2027 are 8 and 5.6 nm, respectively. Thus, the technology in 2027 would be something like that of 8 or 6 nm in reality, and people might be disappointed by the fact. Actually, the shrinking rate for one generation of metal line pitch, gate length  $(L_a)$ , supply voltage  $(V_{supply})$ , equivalent gate oxide thickness (tox), and Si layer thickness (tsi) for SOI and fin-FET, are expected to be much larger and 0.80, 0.83. 0.96, 0.91 and 0.84, respectively. In fact, the physical

| Table 1. Past technology generations for MOSLSIs.                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (1970) 10 $\mu$ m $\rightarrow$ 8 $\mu$ m $\rightarrow$ 6 $\mu$ m $\rightarrow$ 4 $\mu$ m $\rightarrow$ 3 $\mu$ m $\rightarrow$ 2 $\mu$ m $\rightarrow$ 1.2 $\mu$ m $\rightarrow$   |

| $0.8 \ \mu\text{m} \rightarrow 0.5 \ \mu\text{m} \rightarrow 0.35 \ \mu\text{m} \rightarrow 0.25 \ \mu\text{m} \rightarrow 180 \ \text{nm} \rightarrow 130 \ \text{nm} \rightarrow$ |

| 90 nm → 65 nm → 45 nm → 32 nm → 22 nm → 14 nm (2014)                                                                                                                                |

gate lengths of 14 nm technologies are already as large as 25 nm in some semiconductor companies.

There are difficult problems waiting us to limit the downsizing. They are 1) difficulty in EUV lithography development, and cost increase for the double/triple/quadruple lithography as the alternate, 2) increase in the leakage current of MOSFETs, 3) decrease in on-current or drivability of MOSFETs, 4) increase in the capacitance and resistance of the interconnects, 5) degradation in variability, reliability and yield.

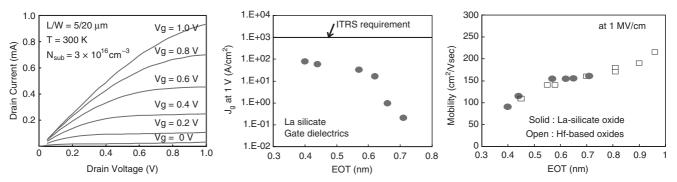

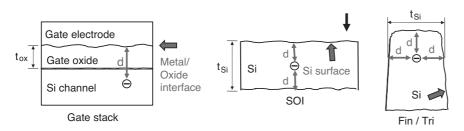

Increase in the leakage current of MOSFETs and decrease in on-current or drivability of MOSFETs can be further explained. With downsizing MOSFETs, four leakage current components of the MOSFETs become problematic; i) punch-through between S (source) and D (drain), ii) direct-tunneling between S and D, iii) subthreshold leakage between S and D, and iv) gate oxide leakage between G (gate) and S, C (channel) and D. Punch-through can be suppressed by controlling the channel potential fixed to 0V, by decreasing V<sub>supply</sub> and t<sub>ox</sub>, and adopting multigate structure (FDSOI-, or fin-FETs) with decreasing t<sub>Si</sub>. Direct tunneling is believed to be the fundamental limit at the gate length of 3 nm. Subthreshold leakage is suppressed by keeping threshold voltage (V<sub>th</sub>) as high as possible, but it is difficult as V<sub>supply</sub> is decreased gradually with the downsizing. In other words, V<sub>supply</sub> reduction is very difficult because V<sub>th</sub> cannot be decreased. Gate oxide leakage is fortunately believed not to become the limiting factor until the '1.3 nm generation' in which  $L_{\alpha}$  and  $t_{ox}$  are assumed to be 5.6 nm and 0.43 nm (EOT), respectively (see Table 2). We have already confirmed the one order of magnitude

| Table 2. Shrink rate of parameters calculated from the data in Table FEP2, ITRS 2013 |                   |           |           |  |

|--------------------------------------------------------------------------------------|-------------------|-----------|-----------|--|

|                                                                                      |                   | Year 2013 | Year 2027 |  |

| Commercial name (nm)                                                                 | imes 0.70/2 years | 14 (nm)   | 1.3 (nm)  |  |

| Metal half pitch (nm)                                                                | imes 0.80/2 years | 40 (nm)   | 8 (nm)    |  |

| L <sub>g</sub> (nm)                                                                  | imes 0.83/2 years | 20.2 (nm) | 5.6 (nm)  |  |

| V <sub>dd</sub> (V)                                                                  | imes 0.96/2 years | 0.86 (V)  | 0.65 (V)  |  |

| EOT (nm)                                                                             | × 0.91/2 years    | 0.80 (nm) | 0.43 (nm) |  |

| T <sub>si</sub> (nm)                                                                 | imes 0.84/2 years | 7.4 (nm)  | 2.0 (nm)  |  |

Fig. 1 0.4 nm EOT High-k MOSFET characteristics; (a) I<sub>d</sub>–V<sub>d</sub> characteristics, (b) gate leakage current vs. EOT, (c) mobility vs. EOT (H. Iwai, Tutorial, ESSDERC 2014).

Fig. 2 Interaction between the channel carriers and interface/surface. The interaction becomes stronger as d becomes smaller with decrease in  $t_{ox}$  and  $t_{Si}$ . (H. Iwai, Tutorial, ESSDERC 2014).

smaller gate leakage current by the experiment of 0.4 nm EOT gate oxide MOSFETs as shown in Fig 1. Among the 4 components, the sub-threshold leakage current will limit the down-sizing, before  $L_g$  reaches 3 nm, especially for mobile applications.

Another big problem is the significant decrease in the on-current of MOSFETs with decrease in  $t_{ox}$  and  $t_{Si}$ . With decrease in these thicknesses, interaction between the carriers and the interface/surface becomes extremely strong as shown in Fig. 2, resulting in the significant decrease in mobility. The reduction of the carrier density under low V<sub>supply</sub>, due to the

decrease in the density of the state (DOS) when decreasing  $t_{Si}$ , is another reason for the on-current reduction.

In conclusion, there is certain high possibility that the downsizing faces its limit in near future because of the increase in the sub-threshold leakage current and lithography process cost, especially in the application of the mobile devices at the gate length of just sub-10 nm. Already its symptom appears in the slowing down of the physical parameter shrinkage rate as shown in Table 2. Recently, there has been a very good challenge in the research of emerging technologies for lower voltage operation, but they are not yet in the stage for the industry to assume them seriously for next future generations.

However, even though, the downsizing of the MOSFETs will stop in some future, it is not necessary to be too pessimistic. The demand and market size for the microprocessors will keep increasing in future smart society, and thus, the effort to further enhance the performance, and to decrease the power consumption and production cost will be and should be continued even after the 'end of miniaturization.'

Hiroshi Iwai worked on the development of wide ranges of semiconductor technologies and products for 26 years at Toshiba Corporation

since 1973, and for 15 years at Tokyo Institute of Technology since 1999.

> Hiroshi Iwai Tokyo Institute of Technology Yokohama, Japan iwai.h.aa@m.titech.ac.jp

# 2014 IEEE INTERNATIONAL ELECTRON DEVICES MEETING HIGHLIGHTS

The 60th annual IEEE International Electron Devices Meeting, held in San Francisco from December 15-17, 2014, was attended by some 1,625 of the world's leading scientists, engineers and researchers, who participated in more than 200 technical presentations on the latest developments in advanced semiconductor technology, power devices, novel memory structures, and the medical application of MEMS and other electronic technologies. The conference was preceded by a day of short courses, and a half-day of tutorial sessions.

Among the highlights of the technical program were two late-news papers on 14nm FinFET processes, presented by Intel (employing novel sub-fin doping and air-gapped interconnects on bulk silicon substrates, with ultra-dense SRAM cells for cache memory); and IBM (using a process with 15 levels of copper and embedded DRAM on a silicon-on-insulator substrate). Both presentations, as well as those by TSMC and other chipmakers, indicate that the industry is keeping pace with Moore's Law using FinFET technology.

Power electronics were another highlight of the conference, with the opening plenary talk by Cree's CTO John Palmour detailing progress being made in the area of wide bandgap power devices, specifically thirdgeneration silicon carbide power MOSFETs as well as SiC IGBTs and GTOs ranging from 900V to 27kV, with applications in electric trains and advanced electric grid equipment. In another power talk, NCSU's Dr. Jayant Baliga described the societal impact of advanced power electronic devices-specifically IGBTsin reducing global electricity consumption by some 50,000 terawatthours over the last 25 years.

The expanding medical applications of bio-sensors and MEMS/NEMS

technology were well-represented, with a paper from the University of Tokyo describing a MEMS tweezer capable of selecting individual DNA molecules for on-chip real-time analysis, which has application in detecting mutated proteins thought to be related to Alzheimer's disease. In another DNA-related paper, Dr. Annette Grot of Pacific Biosciences described the development of high-resolution, high-speed CCD and CMOS image sensors capable of reading optical tags placed on DNA nucleotides, enabling faster and lower-cost DNA sequencing.

Breakthroughs in carbon nanotube array density were presented by researchers from Stanford University, with the first demonstration of highly aligned carbon nanotube FETs with a density of more than 100 CNTs/µm and drive currents similar to scaled silicon FETs. Their parallel alignment and density was made possible by a new multiple-CNT transfer technique. Another novel manufacturing process was demonstrated by a team from imec, with a programmable 2.1 kHz, 8-bit microprocessor constructed of thin-film transistors inkjet-printed on plastic, expected to be used in RFID and NFC applications.

Other highlights of IEDM included a Tuesday luncheon address by Cypress Semiconductor CEO/Founder, Dr. T.J. Rodgers, who advocated an alternative view of the causal relationship between CO<sub>2</sub> levels and global temperature patterns, and advised green energy companies to engineer their products to succeed in the marketplace without government subsidies. At the Wednesday Entrepreneurs luncheon, cosponsored by IEDM & EDS Women in Engineering, Kathryn Kranen, former President/CEO of Jasper Design Automation, shared her advice on establishing a successful startup business in technology. And a special evening panel discussion focused on the past 60 years of innovation at IEDM, and asked the distinguished panel of technology experts to imagine what the next 60 years would reveal.

Next year's IEDM will be held December 7–9, 2015, at the Washington Hilton in Washington, DC. Starting in 2016, the conference will be held in San Francisco, California, each year.

The 2014 IEDM opening plenary talk given by Cree's CTO John Palmour

# UPCOMING TECHNICAL MEETINGS

# 2015 IEEE PHOTOVOLTAIC SPECIALISTS CONFERENCE (PVSC)

We invite you to join us for the 42nd IEEE Photovoltaic Specialists Conference (PVSC), being held June 14–19, 2015, in New Orleans, Louisiana. Since our first meeting in 1961, the PVSC has established itself as the world's leading technical event for scientists, engineers and decisionmakers across the full spectrum of PV technologies. As PV technologies continue to leap forward at an unprecedented pace, we are expecting yet another tremendous conference.

#### 42nd IEEE PVSC Highlights

#### Tutorials

The week will begin with a series of educational sessions on PV technologies and markets. These half-day tutorials will offer valuable insights for everyone from industry newcomers who may appreciate the "Photovoltaics 101" sessions, to veterans looking to expand their understanding in new areas, such as Si experts looking to learn how a multi-junction solar cell works. These courses will provide a focused, rapid education in a range of topics of interest to the PV community.

#### **Technical Program**

Above all, the PVSC is renowned for its one-of-a-kind technical program, where the world's leading voices in PV present their latest findings and offer forward-looking insights on the future of the industry. For the 42nd meeting, we are expecting over 1,100 submissions, which will bring you an unparalleled educational experience across 11 topical areas:

Area 1. Fundamentals and New Concepts for Future Technologies

Area 2. Chalcogenide Thin Film Solar Cells

Area 3. III-V and Concentrator Technologies

*Area 4.* Crystalline Silicon Photovoltaics *Area 5.* Thin Film Silicon Based PV Technologies

Area 6. Organic, Perovskite, and Hybrid Solar Cells

Area 7. Space Technologies

Area 8. Characterization Methods Area 9. PV Modules, Manufacturing,

Systems and Applications

Area 10. PV Deployment and Sustainability

Area 11. PV Reliability

Our technology focus spans from the basic technologies through system development and characterization, to deployment. The PVSC is the only PV technology conference that maintains a focus on space technologies in Area 7, which is the birthplace of PV for electric energy generation and continues as the incubator for high efficiency technologies. Areas 9 through 11 form our PV system development and deployment thrust in which we track the transition of PV technologies from development to use in the field and analyze the onstation performance.

The PVSC Exhibit hall will be providing an action-packed floorshow with an extensive list of companies eager to interface with the PV specialists at the conference. Being the premier technical PV conference, the exhibiters will be those serving the needs of the PV specialist, displaying the latest in solar simulator capability, electrical material characterization, semiconductor growth tools, and many more.

PVSC endeavors to foster as much student participation as possible. We facilitate access to the conference with a reduced student registration rate, and the graduate student assistant program, and we strive to enhance the student's conference experience with events like our student mixer and the best student paper award. We also maintain our PV Jobs portal, which is of keen interest to our students and to our community as a whole.

The IEEE PVSC 42 is shaping up to be our most exciting conference yet, so be on the look-out for our First Call for Papers and mark your calendar for the abstract submission deadline of January 23, 2015 and the conference date of June 14–19, 2015. For more information, visit the conference website: http://www.ieeepvsc.org/PVSC42/.

> Robert J. Walters 2015 PVSC Publicity Chair NRL

Rebekah Feist 2015 PVSC Deputy Publicity Chair The Dow Chemical Company

# 2015 IEEE INTERNATIONAL VACUUM ELECTRONICS CONFERENCE (IVEC)

We are very pleased to announce that the Sixteenth International Vacuum Electronics Conference (IVEC2015) will be held April 27-29, 2015, at Beijing International Convention Center (BICC), Beijing, China. Visitors from around the world will experience its long historic, royal architectures and gardens such as the Forbidden City, the Temple of Heaven, the magnificent Ming Tombs, the Summer Palace, the Great Wall, as well as its great changes in the past three decades, particularly the new buildings including the Bird Nest National Stadium and Water Cube Swimming Center for the 2008 Olympic games and also the 2014APEC Venues which is within walking distance. Beijing is the scientific, educational and cultural heart as well as a key transportation hub which supplies direct flights to most of domestic and international cities.

With technical co-sponsorship from the IEEE Electron Devices Society, the conference will provide a forum for scientists and engineers from all over the globe to present the latest development in vacuum electronics at frequencies ranging from UHF to Terahertz frequency band, as well as their applications.

IVEC was originally created in 2000 by merging the US PowerTubes Conferences and the Europe Space AgencyTWTA Workshops. Now a fully international conference, IVEC is held every other year in the US and in Europe and Asia alternately every fourth year. After the successful and enjoyable IVEC2014 in Monterey, California, IVEC2015 will come to Beijing, China, the first Chinese edition of IVEC after IVEC2003 in Seoul, Korea, IVEC2007 Kitakyushu, Japan and IVEC2011 in Bangalore, India.

IVEC2015 will last three days with one plenary session on the first day and around 30 technical oral and poster sessions planned for the remaining two and half days. Technical presentations spans the range from UHF to THz frequencies, presenting current work in theory and computational tool development, active and passive components, systems, and supporting technologies. Developers of systems will find that IVEC provides a unique snapshot into the current state-of-the-art in vacuum electronic devices. These devices continue to provide unmatched power and performance for advanced electromagnetic systems, particularly in the challenging frequency regimes of millimeter-wave and THz electronics. The meeting is configured to maximally disseminate useful information to device users, manufacturers, academics, and students.

IVEC2015 plenary talks will give the latest progress in the theory and technologies of high frequency and high power vacuum devices, and also provide insights into the broad spectrum of scientific issues and applications that are driving the current directions in vacuum electronics research. There will be a number of topical scientific and commercial applications highlighted, including fusion energy, medical applications, and RF accelerator technology for high energy physics. From this conference you can have a panorama view of vacuum electronics in Asia, especially China for both education and industry.

The John R. Pierce Award for Excellence in Vacuum Electronics and a Student Paper Award will be presented and as in the past, the meeting and social events will provide unique opportunities to renew or establish new friendships with colleagues, interact with customers, end-users, and meet students and academic researchers.

The conference website is the best source of information about IVEC2015, including Technical Areas, Paper Submission, Registration, Accommodation, and other important dates and events. Please visit http://cie-china.org/ivec2015 for more details and latest news about the conference. To enquire about exhibitor space and conference support, please contact Dr. Jinjun Feng (fengjj@ieee.org).

You can also learn more about IVEC by visiting the IEEE EDS Vacuum Electronics Technical Committee website: http://www.vacuumelectronics. org.

We look forward to seeing you in Beijing.

Jinjun Feng 2015 IVEC Technical Program Chair Beijing Vacuum Electronics Research Institute Beijing, China

# Society News

#### EDS PRESIDENT'S MESSAGE

Albert Wang EDS President

Organized concurrently with the Region 9 Chapter Meeting Series, this marks the first EDS ExCom meeting ever held in South America. For more coverage of the R9 Chapter Meeting, see page **29**.

**Dear Fellow**

**EDS Members**,

On September 20,

2014, an EDS Ex-

Com meeting was

held at the Uni-

versidad Tecno-

logica de Bolivar,

in Cartagena de

Indias, Colombia.

Over the past few years, EDS's activities in R9 have been blooming thanks to the great efforts of the local SRC leadership team and, more critically, the EDS members in the region. Outreach programs such as Engineers Demonstrating Science: an Engineer Teacher Connection (EDS-ETC), have been very successful in advancing EDS's mission in Central and South America. Thanks to these efforts, there are now 22 EDS chapters in Region 9! Having the ExCom meeting in Cartagena, Colombia, is a strong endorsement of the Society's activities in Region 9 and I offer special thanks to EDS Secretary Fernando Guarín and the leadership team led by R9 SRC Chair Jacobus Swart.

Many key issues were discussed at the ExCom meeting and action plans were developed accordingly. Bin Zhao, our VP for Publications and Products, provided a detailed analysis of the possible impact the global trend toward open-access (OA) will have on EDS's publication revenue and offered insights on how to best integrate OA into the Society's publication operations. Because publications are a foundational element of what EDS provides its members and the larger technical community, we must do all we can to enhance the quality and accessibility of our technical journals.

Several other items were discussed at the ExCom meeting. I am pleased to announce that you will soon enjoy a new e-Version of the EDS Newsletter. This will not only help transition the Newsletter from the paper format to a fully digital format, but it's far more environmentally friendly.

Regarding Membership and Services, we discussed two options to help make joining EDS more affordable: Society Affiliate membership and the IEEE e-Membership. Promoting affiliate membership will be a key focus going forward. In addition to providing an affordable option for joining EDS, this will help us facilitate collaboration with other technical societies and organizations. For our members in the developing world, IEEE e-Membership significantly reduces the cost of membership in the IEEE and EDS from about \$200 to \$90.

Leda Lunardi, EDS VP of Technical Committees and Meetings, discussed the action plans to improve technical committee activities, the new technical committee survey, her on-going evaluation of all EDS-sponsored conferences, and the possibility of merging and/or co-locating some of EDS's smaller conferences. With about 80 financially and technically sponsored conferences, it is critical that we frequently review the society's conference portfolio to ensure not only technical coverage of current and emerging trends, but also the fiscal health of our technical meetings.

I will continuously report all EDS activities to you. Meanwhile, it is important that I hear from you, our dear EDS members. So for any ideas, suggestions, and complaints aimed at helping to improve the EDS community, please write to me at eds@ieee.org. The EDS leadership team and I have our ears wide open!

> Sincerely, Albert Wang from Southern California

# MESSAGE FROM EDS VICE PRESIDENT OF TECHNICAL COMMITTEES AND MEETINGS

Leda Lunardi EDS Vice President of Technical Committees and Meetings

It is my pleasure to write to you as the Vice President of Technical Committees and Meetings, and an elected member of the EDS Board of Governors since January 1, 2014. Having joined IEEE as a student member over 30 years

ago, I have greatly enjoyed the benefits of the EDS network: strong partnerships, loyal friends, and being a part of the global EDS community of dedicated professionals. Among the latter are the members of the technical committees (TCs) which form the core of EDS's conferences, meetings, and publications. Presently there are 14TCs assembled in areas of EDS interest ranging from conventional topics (such as Semiconductor Devices, Compact Modeling, Device Reliability Physics, Power Devices and Integrated Circuits, VLSI Technology and Circuits, Semiconductor Manufacturing), through applied areas (TCAD), and multidisciplinary areas (Electronic Materials, MEMS, and Optoelectronic Devices) and more emerging areas (Organic devices, Nanotechnology).

In close partnership with the EDS staff, the leadership of the technical committees and their members have spent a great deal of time in the past year reviewing requests for new or renewed EDS technical sponsorship of meetings and conferences. Presently EDS sponsors over 67 technical meetings. With such a large and diverse conference portfolio, the expertise of the TC members has been essential in reviewing these requests and recommending alternatives addressing meetings and conferences that consistently underperform financially or in terms of attendance.

As a volunteer-driven society we continuously seek and support suggestions from TC members related to new or emerging areas that could be of interest for an EDS-sponsored workshop, mini-symposia or webinar. This could also include topics for special issues or focused papers for any of the journals and magazines that the society sponsors. For instance, early this year on May 2014 the Optoelectronic Devices Committee Chair TC chair successfully proposed a special issue for the IEEE Journal of Lightwave Technology on "Semiconducting Optoelectronic Materials and Devices for Energy Conversion," with publication date planned for November/December of 2015.

As we implement different activities in each respective technical area or when collaborating with other technical societies the feedback from members like you is vital. Please let us know your ideas and suggestions, preferably by email to me (leda\_ lunardi@ncsu.edu) or Ms. Jean Bae, the EDS Senior Conference Administrator (jean.bae@ieee.org).

> Sincerely yours, Leda Lunardi North Carolina State University Raleigh, NC, USA

M K Radhakrishnan Editor-in Chief EDS Newsletter

#### introduce.

We have two articles in ourTechnical Briefs Section, one featuring the latest trends in Silicon Device Scaling and the other on "Blue LED", which elicited in the 2014 Physics Nobel Prize. A short feature on the Nobel Prize winners is given in the Technical Briefs section. In our Chapter News section, one of our enthusiastic Student Chapter's Vacation Project Mania is featured, which has evaded students from nearby institutions in enjoying the vacation outside and tied down to the campus to enhance engineering innovation. Our Newsletter team would like to hear your views about the contents and suggestions to improve.

Readers' feedback is very important in the growth of our Newsletter. We always like to hear from our members, and the editorial team is looking for constructive criticisms. Please use the e-mail edsnewsletter@ieee.org to convey your ideas and feedback.

Two of our Regional Editors, Fernando Guarín (Regions 1, 2 & 3) and Francisco Sanchez (Region 9) are leaving the team. Fernando being the EDS Secretary and Chairman of EDS Newsletter Oversight Committee is an ardent volunteer guiding and supporting all the developments in the Newsletter and EDS. Francisco has extended the communication between Chapters provided unprecedented exposure to activities of Chapters in Latin America during his tenure as Editor. On behalf of our entire Newsletter team, I would like to express our sincere gratitude to both Fernando and Francisco.

Four new members are joining our Editorial team, out of which

#### Message from Editor-IN CHIEF

Dear Readers,

Best Wishes for a

Happy New Year

2015. This issue of

our Newsletter has

many interesting

features in contents. Also, we have four

new members in

our Editorial team,

whom I am glad to

two are women volunteers. Mukta Faroog from IBM will be the Editor for Regions 1, 2 & 3. Joao Antonio Martino of University of Sao Paulo, Brazil is the new Regional Editor for Region 9 – Latin America. In the Region 10 (Australia, New Zealand & South Asia), now we have two Editors in place of my position as Regional Editor. Susthitha Menon from University Kebangsaan Malaysia is the new Regional Editor for Australia and South East Asia in Region 10. Manoj Saxena from University of Delhi is the new Editor for South Asia in Region 10. It is my pleasure to welcome all of them to our team as new Editors of the EDS Newsletter.

Mukta Farooq is an expert metallurgist and materials scientist at the IBM Systems and Technology Group at East Fishkill, New York.

Her areas of expertise include 3 Dimensional silicon integration and packaging, die and wafer stacking for hybrid memory cube and other applications, CMOS FET back end of line structures, flip-chip/C4 technology, lead-free alloys, chip package interaction, and intellectual property.

Mukta is a prolific inventor with over 168 issued U.S. and international patents. She has been designated an IBM Lifetime Master Inventor because of her sustained contributions to intellectual property. She has also authored 25 external publications and has given invited talks at various conferences and universities. Mukta is a founding member of the IBM Semiconductor Technology Symposium held annually, and has served as Technical Chair and General Chair. She is a Senior Member of IEEE, a Distinguished Lecturer of the IEEE EDS, and the Chair of the IEEE EDS Mid-Hudson Valley Chapter.

Mukta is currently a SeniorTechnical Staff Member at IBM. She has a B.Tech in Metallurgical Engineering from IIT Bombay, an M.S. in Materials Science from Northwestern University, Evanston, Illinois, and a Ph.D. in Materials Science & Engineering from Rensselaer Polytechnic Institute, Troy, New York.

Joao Antonio Martino is currently a full professor and the head of SOI group at University of Sao Paulo, Brazil. He received mas-

ters (1984) and PhD (1988) degrees in microelectronics from University of Sao Paulo. He was a postdoctoral researcher in silicon-on-insulator (SOI) devices and technology in IMEC, Belgium. His expertise is in electrical characterization, simulation and modeling of SOI devices in wide temperature range. He is also interested in the SOI-CMOS fabrication process, multiple-gate devices (FinFET), 1T-DRAM, Tunnel-FET and radiation effects. He has authored or coauthored of more than 400 technical journal papers and conference presentation and author/ editor of 5 books. He is senior member of IEEE and distinguished lecturer of the IEEE Electron Device Society (EDS). He is chair of IEEE ED South Brazil Chapter and vice-chair of Region 9 SRC of IEEE EDS.

P Susthitha Menon is currently an Associate Professor at the Universiti Kebangsaan Malaysia (UKM) at Kuala Lumpur. She received her

BSEE degree from (UKM) in 1998. As an Intel scholar, she worked at Intel Malaysia as a Product Engineer for mobile modules systems from 1999 to 2002. She then received her MSc and PhD (Distinction) degrees in 2005 and 2008 respectively from UKM, for the development of Si- and InGaAs-based interdigitated p-i-n photodiodes. At the University's Institute of Micro-Engineering & Nanoelectronics (IMEN) she is specializing in the field of optoelectronics, nanophotonics, and robust engineering optimization. Susthitha is a Senior Member of IEEE. She is in the organizing team international conference ICSE by ED Malaysia Chapter for many years and is the Secretary of the IEEE Electron Devices Malaysia Chapter.

Manoj Saxena is an Associate Professor in Department of Electronics, Deen Dayal Upadhyaya College, University of Delhi, New Delhi, India.

He received B.Sc. (with honors), M. Sc., and Ph.D. degrees from the University of Delhi in 1998, 2000, and 2006 respectively. He has authored or coauthored 190 technical papers in international journals and various international and national conferences. His current research interests are in the areas of analytical modeling, design, and simulation of Optically controlled MESFET/MOSFET, silicon-on-nothing, insulated-shallowextension, grooved/concave-gate MOSFETs, cylindrical gate MOSFET and Tunnel FET. He is a reviewer to many journals including Solid State Electronics, Journal of Physics: D Applied Physics and IEEETED and EDL.

Manoj is a Senior Member of IEEE and also Member of Institute of Physics (UK), Institution of Engineering and Technology (UK), National Academy of Sciences India (NASI) and International Association of Engineers (Hong Kong). Currently, he is the Secretary of EDS Delhi Chapter. For his voluntary contribution, Manoj received the outstanding EDS Volunteer recognition from EDS Chapters in the region in 2012.

> M K Radhakrishnan Editor-in Chief, EDS Newsletter e-mail: radhakrishnan@ieee.org

# CALL FOR NOMINATIONS IEEE FELLOW CLASS OF 2016

IEEE Fellow is a distinction reserved for select IEEE members. The honor is conferred by the Board of Directors upon a person with an extraordinary record of accomplishments in any of the IEEE fields of interest.

If you know of an IEEE colleague who is a Senior Member or Life Senior Member in good standing, has completed five years of service in any grade of IEEE Membership and who has made an outstanding contribution to the electronic or electrical engineering profession in any of the IEEE fields of interest, you can nominate this person in one of four categories: Application Engineer/Practitioner, Educator, Research Engineer/Scientist or Technical Leader.

Nominations for the Fellow Class of 2016 are now being accepted.

To learn more about the Fellow program and the application process, visit the Fellow Web Site at http:// www.ieee.org/fellows. The deadline for nominations is 1 March 2015.

Some of the IEEE Fellows who were honored at the 2013 IEDM Plenary.

# CONGRATULATIONS TO THE 34 EDS MEMBERS RECENTLY ELECTED TO IEEE SENIOR MEMBER GRADE!

Meng-Fan Chang Victor Corasaniti E. Cowell, III Xiaoli Feng Wolf Fischer Akira Fujiwara Steven Galecki Nima Ghalichechian Daniel Green Fawnizu Azmadi Hussin John Jackson Noor Ain Kamsani Curt Karnstedt Seongsin Kim Stephen Kosonocky Mohdkhairuddin Mdarshad David Meyer Ivona Mitrovic Joel Molina Martin Mollat Macaulay Osaisai Michael Piszczor Ali Razavieh Patrick Roblin Michael Ropp Suba Subramaniam MichaelTan VivekTD RaviTodi AkiraToriumi ReydezelTorres-Torres EricTournie Zhijian Xie WoojunYoon

For more information on senior member status, visit: http://www.ieee.org/membership\_services/membership/ senior/index.html

To apply for senior member status, fill out the on-line application: https://www.ieee.org/membership\_services/ membership/senior/application/index.html.

You will need to Sign-in with your IEEE account.

#### Please remember to designate the Electron Devices Society as your nominating entity!

employers, recognizing this new status.

If you have been in professional practice for 10 years,

you may be eligible for Senior Membership, the highest

grade of membership for which an individual can apply.

New senior members receive a wood and bronze plaque

and a credit certificate for up to US\$25 for a new IEEE

society membership. Upon request a letter will be sent to

#### 2013 EDS GEORGE E. SMITH AWARD

A high priority of the Electron Devices Society (EDS) is to recognize and enhance the quality of papers published in EDS archival literature. The George E. Smith Award was established in 2002 to recognize the best paper appearing in a fast turnaround archival publication of EDS, targeted to *IEEE Electron Device Letters*. Among other criteria including technical excellence, an important metric for selection for the award is comprehensive and impartial referencing of prior art.

The papers winning the 2013 George E. Smith Award were selected from among 480 articles that were published in 2013. The articles are entitled "Origins of Effective Work Function Roll-Off Behavior for High-k Last Replacement Metal Gate Stacks," along with the paper entitled, "Flexible Complementary Logic Gates Using Inkjet-Printed Polymer Field-Effect Transistors." These papers appeared in the June 2013 and January 2013 issues of Electron Device Letters and were authored by Takashi Ando, Eduard A. Cartier, John Bruley, Kisik Choi, Vijay Narayanan, along with Yong-Young Noh, Kang-Jun Baeg, Dongyoon Khim, Juhwan Kim, Dong-Yu Kim, Si-Woo Sung, and Byung-Do Yang.

The award will be presented at the plenary session of the IEEE International Electron Devices Meeting to be held on December 15, 2014 in San Francisco, California. In addition to the award certificate, the authors will receive a check for \$2,500 to be shared equally among all authors. On behalf of the Electron Devices Society I would like to congratulate the authors for this achievement. Brief biographies of the authors follow.

Takashi Ando received the B.S. and M.E. degrees from the University of Tokyo and the Ph.D. degree from Osaka University in 1999, 2001, and 2010, respectively. He has been a Research Staff Member with the IBM T. J. Watson Research Center, Yorktown Heights, New York, USA, since 2008.

Eduard Cartier earned his Ph.D from ETH Zurich, did research at ETH and ABB Research in Switzerland. Since 1989 he is RSM at the

IBM T.J. Watson Research in New York, USA, where he works on dielectric degradation and on HK/MG development for advanced CMOS technologies.

John Bruley earned his Ph.D. in Physics from Cambridge University (1988). He held positions at the Max-Planck-Institute for Metals

Research in Stuttgart and the Materials department at Lehigh University. He is currently a senior engineer at IBM's T.J. Watson Research Center. He was recipient of the Microbeam Analysis Society's "Heinrich Award" in 1999.

Kisik Choi is currently a Research Fellow at SK hynix. He contributed to the development of gate stack technologies at IBMT. J. Watson

Research Center in Yorktown Heights, New York, as an assignee of GLOBAL-FOUNDRIES. Dr. Choi earned BS and MS in Materials Engineering from Seoul National University and a Ph.D. in Electrical Engineering from Texas Tech University.

Vijay Narayanan

received the B.Tech. degree in Metallurgical engineering from IIT Madras, India, and the M.S. and Ph.D. degrees in Materials Sci-

ence and Engineering from Carnegie Mellon University, in 1995, 1996, and 1999, respectively. He joined IBM Research in 2001, where he conducts research on gate-stacks for CMOS Logic. Dr. Narayanan is a fellow of the American Physical Society.

Yong-Young Noh is Associate Professor at Dongguk University in Seoul, South Korea. He received Ph.D. at GIST (2005) and

worked at the Cavendish Laboratory, ETRI, and Hanbat National University. He has received Merck Young Scientist Award (2013) and Korea President Award (2014). His current interest is in printed transistors.

Kang-Jun Baeg is a senior research scientist at Korea Electrotechnology Research Institute. He received his Ph.D. in materials science and engi-

neering from GIST (Korea) in 2010, was a member of engineering staff in ETRI (Korea) from 2010 to 2011, and a postdoctoral research fellow in chemistry at Northwestern University. (in 2012).

Dongyoon Khim received the BS in electronical engineering from Sungkyunkwan University, Korea, in 2008, and the MS and Ph.D. in material science engineering from the Gwangju Institute of Science and Technology, Korea, in 2009 and 2014, respectively. He has worked at Dongguk Univeristy as a postdoctoral research fellow since 2014. His current research interests include the printed electronic devices.

Juhwan Kim received his Ph.D. degree in Materials Science and Engineering from Gwangju Institute Science and Technology in 2013, and

is currently a postdoctoral researcher at Gwangju Institute Science and Technology. His research interest is focused on the synthesis of polymers and carbon based materials and their incorporation into electronic devices.

**Dong-Yu Kim** is Professor of Materials Science and Engineering at Gwangju Institute of Science and Technology,

Republic of Korea. He received Ph.D. at University of Massachusetts Lowell in 1997 and he is a fellow of the Korean Academy of Sci-

ence and Technology. His research interest covers materials and devices for organic electronics, publishing over 200 papers, with H-index above 40.

Si-Woo Sung received B.E. degree in Electronic Engineering and M.S. degree in Semiconductor Engineering from Chungbuk Na-Papublic of Korca

tional University, Republic of Korea, in 2010 and 2012, respectively. He is an engineer at ADtech, Cheongju, Republic of Korea. His research interests include organic-TFT circuit design and power IC designs.

Byung-Do Yang received the B.S., M.S., and Ph.D. degrees in Electrical Engineering and Computer Science from KAIST, Republic of Ko-

rea, in 1999, 2001, and 2005, respectively. He was a senior engineer at the Memory Division, Samsung Electronics, Kyungki-Do, Republic of Korea, in 2005, where he was involved in the design of DRAM. In 2006, he joined the Department of Electronics Engineering, Chungbuk National University, Republic of Korea, where he is currently an Associate Professor. His research interests are analog circuit, memory circuit, and power IC designs.

Bin Zhao EDS Vice President of Publications Fairchild Semiconductor Irvine, CA, USA

### 2013 EDS PAUL RAPPAPORT AWARD

A high priority of the Electron Devices Society is to recognize and enhance the quality of papers published in EDS archival literature. Every year, the Society confers its prestigious Paul Rappaport Award to the best paper published in the IEEE Transactions on Electron Devices. Among other criteria including technical excellence, an important metric for selection for the award is comprehensive and impartial referencing of prior art. The winning paper was selected from close to 600 articles that were published in 2013. The winning paper is entitled, "High-Mobility Ge p- and n-MOSFETs With 0.7-nm EOT Using HfO2/Al2O3/ GeOx/Ge Gate Stacks Fabricated by Plasma Postoxidation." This paper was published in the March, 2013 issue of the IEEE Transactions on Electron Devices, and was authored by Rui Zhang, Po-Chin Huang, Ju-Chin Lin, Noriyuki Taoka, Mitsuru Takenaka, and Shinichi Takagi.

The award will be presented at the plenary session of the IEEE International Electron Devices Meeting to be held on December 15, 2014, in San Francisco, California. In addition to the award certificate, the authors will receive a check for \$2,500 to be shared equally among all authors. On behalf of the Electron Devices Society, I would like to congratulate the authors for this achievement. Brief biographies of the authors follow.

**Rui Zhang** received B.E. and M.E. degrees in materials science and engineering from Tsinghua University, China in 2006 and 2009,

and Ph.D. degree in electrical engineering from University of Tokyo, Japan in 2012. He is currently an assistant professor with Department of Information Science and Electronic Engineering, Zhejiang University, China.

**Po-Chin Huang** received the Ph.D. degree from the Institute of Microelectronics, National Cheng Kung University, Taiwan in 2012.

He was a cooperated researcher in the School of Engineering, University of Tokyo, Japan during 2011 to 2012. Currently, he returned to National Cheng Kung University as a postdoctoral research fellow.

Ju-Chin Lin was born in Taichung, Taiwan, on November 8, 1987. She received the B.S. degree in electrophysics from National Chiao

Tung University, Taiwan, in 2011, and the M.S. degree in electrical engineering from the University of Tokyo, Japan, in 2013. She joined Mitsubishi Electric Corporation, Japan in 2014.

Noriyuki Taoka received Ph.D degree in engineering from Nagoya University, Nagoya, Japan in 2005. From 2005 to 2010, he had

engaged in research of Ge devices in MIRAI project and in the research of III-V & Ge devices at the University of Tokyo, from 2010 to 2011. More recently, in 2012 to 2014, he was involved in the research of IV-IV-alloy systems for electron and optical devices, as an associated professor of Nagoya University. Since 2014, he has been at IHP, Germany, participating in research of IV-IV-alloy systems.

**Mitsuru Takenaka** received B.E., M.E., and Ph.D. degrees in electronic engineering from the University of Tokyo,

Japan, in 1998, 2000, and 2003, respectively. He is currently an associate professor with the Department of Electrical Engineering and Informa-

tion Systems, the University of Tokyo.

Shinichi Takagi received the B.S., M.S. and Ph.D. degrees in electronic engineering from the University of Tokyo in 1982, 1984 and 1987, respec-

tively. He joined the Toshiba R&D Center in 1987. In 2003, he moved to the University of Tokyo as a professor in the School of Engineering.

Bin Zhao EDS Vice President of Publications Fairchild Semiconductor Irvine, CA, USA

# 2015 PhD Student Fellowship

**Description:** One year fellowships awarded to promote, recognize, and support PhD level study and research within the Electron Devices Society's field of interest. The field of interest for EDS is all aspects of engineering, physics, theory, experiment and simulation of electron and ion devices involving insulators, metals, organic materials, plasmas, semiconductors, quantum-effect materials, vacuum, and emerging materials. Specific applications of these devices include bioelectronics, biomedical, computation, communications, displays, electro and micro mechanics, imaging, micro actuators, optical, photovoltaics, power, sensors and signal processing.

It is expected that three fellowships will be awarded, with the intention of at least one fellowship being given to eligible students in each of the following geographical regions every year: Americas, Europe/Middle East/Africa, and Asia & Pacific. Only one candidate can win per educational institution.

**Prize:** US\$5,000 to the student and if necessary funds are also available to assist in covering travel and accommodation costs for each recipient to attend the EDS Administrative Committee meeting for presentation of the award plaque. The EDS Newsletter will feature articles about the EDS PhD Fellows and their work over the course of the next year.

**Eligibility:** Candidate must be an IEEE EDS student member at the time of nomination; be pursuing a doctorate degree within the EDS field of interest on a full-time basis; and continue his/her studies at the current institution with the same faculty advisor for twelve months after receipt of award. Nominator must be an IEEE EDS member. Previous award winners are ineligible.

**Basis for Judging:** Demonstration of his/her significant ability to perform independent research in the fields of electron devices and a proven history of academic excellence.

#### **Nomination Package**

- Nomination letter from an EDS member

- Two-page (maximum) statement by the student describing his or her education and research interests, accomplishments and graduation date

- One-page biographical sketch of the student (including student's mailing address and email address)

- One copy of the student's under-graduate and graduate transcripts/grades. Please provide an explanation of the grading system if different from the A-F format.

- Two letters of recommendation from individuals familiar with the student's research and educational credentials. Letters of recommendation cannot be from the nominator.

#### Timetable

- Completed nomination packages are due at the EDS Executive Office no later than May 15, 2015

- Recipients will be notified by July 15

- Monetary awards will be given by August 15

- Formal award presentation will take place at the EDS Board of Governors Meeting in December

# EDS is now accepting nomination package submissions via e-mail, fax and mail!

Email: <a href="mailto:edsfellowship@jeee.org">edsfellowship@jeee.org</a> Fax: +1-732-235-1626

#### Mail:

IEEE EDS Executive Office PhD Student Fellowship Program 445 Hoes Lane, Piscataway, NJ 08854 USA

For more information contact: edsfellowship@ieee.org

#### Visit the EDS website:

http://eds.ieee.org/eds-phd-student-fellowship.html

# **2015 Masters Student Fellowship**

**Description:** One-year fellowships awarded to promote, recognize, and support graduate Masters level study and research within the Electron Devices Society's field of interest: all aspects of engineering, physics, theory, experiment and simulation of electron and ion devices involving insulators, metals, organic materials, plasmas, semiconductors, quantum-effect materials, vacuum, and emerging materials. Specific applications of these devices include bioelectronics, biomedical, computation, communications, displays, electro and micro mechanics, imaging, micro actuators, optical, photovoltaics, power, sensors and signal processing.

Three fellowships will be awarded, with the intention of at least one fellowship being given to eligible students in each of the following geographical regions every year: Americas, Europe/Mid-East/Africa, Asia & Pacific. Only one candidate can win per educational institution.

**Prize:** US\$2,000 and a plaque to the student, to be presented by the Dean or Department head of the student's enrolled graduate program.

**Eligibility:** Candidate must be an IEEE EDS student member at the time of nomination; be accepted into a graduate program or within the first year of study in a graduate program in an EDS field of interest on a full-time basis; and continue his/her studies at a graduate education institution. Nominator must be an IEEE EDS member and preferably be serving as the candidate's mentor or faculty advisor. Previous award winners are ineligible.

**Basis for Judging:** Demonstration of his/her significant ability to perform research in the fields of electron devices and proven history of academic excellence in engineering and/or physics as well as involved in undergraduate research and/or supervised project.

#### **Nomination Package**

- Nomination letter from an EDS member who served as candidate's mentor or faculty advisor.

- Two-page (maximum) statement by the student describing his or her education and research interests, accomplishments and graduation date. This can include undergraduate, graduate and summer internship research work.

- One-page biographical sketch of the student (including mailing address and e-mail address)

- One copy of the student's transcripts/grades

- One letter of recommendation from an individual familiar with the student's research and educational credentials. Letters of recommendation cannot be from the nominator.

#### Timetable

- Completed nomination packages are due at the EDS Executive Office no later than May 15, 2015

- Recipients will be notified by July 15

- Monetary awards will be presented by the Dean or Department Chair of the recipient's graduate program at the beginning of the next academic term.

# EDS is now accepting nomination package submissions via e-mail, fax and mail!

Email: edsfellowship@ieee.org Fax: +1 732-235-1626

#### Mail:

IEEE EDS Executive Office PhD Student Fellowship Program 445 Hoes Lane, Piscataway, NJ 08854 USA

# For more information contact: edsfellowship@ieee.org

#### Visit the EDS website:

http://eds.ieee.org/eds-masters-student-fellowship.html

# YOUNG PROFESSIONALS

EDS-ETC

Engineers Demonstrating Science: an Engineer Teacher Connection

# ED UNIVERSIDAD SANTO TOMAS STUDENT BRANCH CHAPTER, TUNJA, COLOMBIA

EDS student chapter members from Colombia's "Universidad Santo Tomas" in Tunja, Colombia, along with the technical IEEE EDS/RAS chapter participated in the EDS-ETC program working with public schools in the Boyacá region. These schools are under the State's Ministry of Education and are located in the 123 municipalities of the state, some near the capital city ofTunja, but most are distant, rural areas with difficult access conditions.

Through the Ministry of Education's website, word about the EDS-ETC program was sent, getting the message out to all schools. More than 60 schools responded to this call, expressing interest in holding workshops. Due to the remote locations, a training session at the University's Teacher's College in Tunja was held, with students from our EDS chapter providing the training. We currently have 10 Snap Circuits kits, Model SC-100R, and we loaned two kits per school for a period of two weeks. We have developed workshops for a wide range of students from different grades. Workshops have been conducted in over 20 schools in the State of Boyacá, several teachers and about 1,200 students participating in grades starting from sixth grade (ages 9 and 10 years) to juniors (ages 15 and 16 years). We have found wide acceptance and a growing interest from the children and their teachers and a great tool for learning has

Students at the College of Antonio Ricaurte Villa de Leyva with Dr. Guarin.

IEEE Fellows and EDS Distinguished Lecturers, Hiroshi Iwai and Fernando Guarin (center), at Universidad Santo Tomas.

been transformed into a desire to create groups and seed technology research for overcoming the problems of their region.

On the faculty website we have created a page to disseminate the results of the program and motivate both our students and teachers and college students to participate. The URL is: http://www.ustatunja.edu.co/ ustatunja/index.php/ieee-usta-tunja/ programa-eds-etc.

Fernando Guarin, IEEE Fellow Member, during the video shoot for IEEEtv

For next year we want to continue growing the program, targeting to reach at least 50 more schools, enhancing our relationship with the Ministry of Education and extending the agreement that was implemented this year that led to training with kits and robotics to 20 schools. We plan to migrate to working with microcontrollers and complex platforms such as Arduino. With the support of the Electron Devices Society of the IEEE, we will no doubt achieve these and other goals. Last September 13th and 15th we welcomed the visit of IEEE Fellows and Distinguished Lecturers Hiroshi Iwai and Fernando Guarin, who visited Schools in Villa de Leyva and Tunja and also delivered Distinguished Lectures at our University.

> Ricardo Casallas ED/RA Tunja Chapter Chair Tunja, Colombia

# IEEE STUDENT TRANSITION & ELEVATION PARTNERSHIP (STEP)

IEEE STEP was developed to provide a dynamic program for facilitating the transition from Student member to young professional by introducing the opportunities and benefits of IEEE membership during the onset of a STEM career.

#### STEP funding